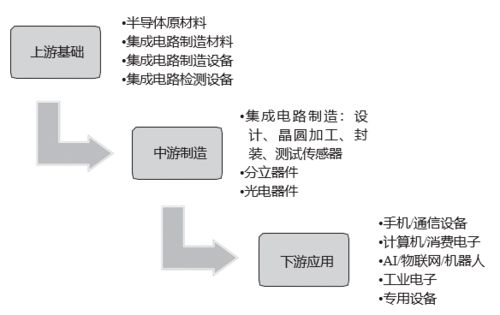

在当今数字化校园建设浪潮中,一个高效、稳定、可扩展的校园网系统是支撑教学、科研、管理与服务的核心基础设施。而作为其硬件基础的集成电路设计,则直接决定了网络的性能、能耗、安全与成本。本文将探讨一套面向校园网系统集成的集成电路设计方案,旨在为构建下一代智慧校园网络提供硬件层面的创新思路。

一、设计目标与原则

本方案的设计目标是为校园网提供高性能、低功耗、高集成度且具备良好可编程性的核心芯片。设计遵循以下原则:

- 高性能与高带宽:必须满足海量终端接入、4K/8K视频流、在线实验平台、虚拟现实教学等高带宽、低延迟应用的需求。核心交换与路由芯片应支持Tbps级别的吞吐能力。

- 高集成度与低功耗:通过先进的半导体工艺(如7nm、5nm),将网络处理单元(NPU)、安全引擎、流量管理单元、多种高速接口(如400G/800G以太网、PCIe)集成于单芯片或芯片组,减少板级互连,降低整体功耗与散热成本,符合绿色校园理念。

- 灵活性与可编程性:采用可编程交换架构(如PISA)或集成可编程内核(如多核ARM/RISC-V),支持通过软件定义网络(SDN)策略动态调整数据平面功能,以适应校园网内科研实验网络、物联网专网、安防监控网等多样化、快速变化的业务需求。

- 内生安全:在芯片内部集成硬件级安全模块,支持国密算法、IPSec/SSL硬件加速、深度包检测(DPI)以及针对DDoS攻击的硬件缓解机制,从底层筑牢校园网安全防线。

- 成本可控:在追求性能的通过架构优化和IP核复用,控制芯片设计与制造成本,确保方案在经济性上适用于大范围校园部署。

二、核心芯片架构设计

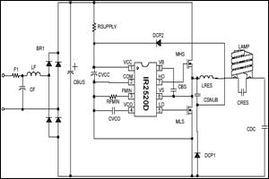

方案的核心是设计一款“校园网智能融合芯片”(Campus Network Intelligent Fusion Chip, CNIFC),其架构可分为以下几个关键部分:

- 高速交换矩阵:采用多级CLOS或交叉开关架构,提供无阻塞、高带宽的内部互联通路,确保所有端口线速转发。

- 异构处理引擎集群:

- 可编程报文处理引擎(PPE):基于P4等语言可编程,负责常规的二三层转发、ACL、QoS策略执行。

- 专用网络处理单元(NPU):针对隧道封装/解封装、网络功能虚拟化(NFV)加速等复杂操作进行硬件优化。

- 多核CPU子系统:集成ARM或RISC-V多核处理器,运行控制平面协议(如BGP、OSPF)、管理软件以及部分用户面轻量级应用。

- 智能加速单元:

- 安全加速引擎:集成密码算法协处理器,支持SM2/SM3/SM4等国密算法及国际标准算法的线速加解密。

- 存储与缓存管理单元:集成大容量、高带宽的片上SRAM与TCAM,并优化与DDR内存控制器的接口,用于转发表、流表及数据缓存。

- 流量管理与调度单元:实现精细化的队列管理、流量整形与调度算法(如WFQ、SP),保障关键业务(如远程教学、视频会议)的服务质量。

- 丰富的高速接口:提供灵活配置的SerDes通道,可捆绑成多种标准接口,包括但不限于:

- 1G/10G/25G/100G/400G以太网端口,用于上行连接与核心互联。

- PCIe Gen4/5接口,用于与服务器、智能网卡或加速卡互联。

- 面向物联网的LPWAN控制器接口(可选)。

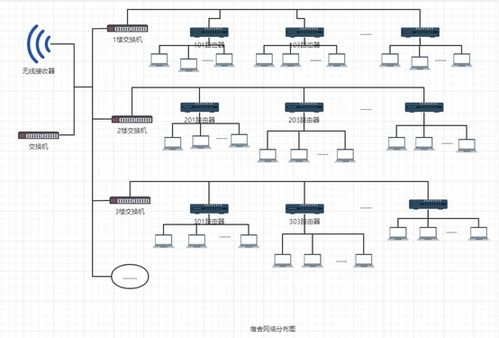

三、系统级集成方案

基于CNIFC芯片,可以构建模块化的校园网设备系列:

- 核心/汇聚交换机:采用多颗CNIFC芯片通过高速互连形成集群,提供超高密度的100G/400G端口,作为校园网的核心骨干。

- 接入交换机/无线控制器:采用单颗或双颗CNIFC芯片,提供高密度的1G/10G/25G下行端口和高速上行,集成无线AC功能,实现有线无线一体化接入与策略统一管理。

- 智能安全网关:强化CNIFC中的安全引擎,并可能集成专用AI协处理器,用于实现基于行为的入侵检测与防御、高级威胁分析等。

- 定制化边缘计算节点:利用CNIFC的可编程性和高速接口,将网络、计算、存储功能在边缘侧融合,为特定院系(如计算机学院、人工智能学院)的科研项目提供灵活的实验平台。

四、设计流程与挑战

本方案的实施需遵循标准的IC设计流程:系统定义、RTL设计、功能验证、综合、布局布线、时序验证、物理验证直至流片。主要挑战包括:

- 设计复杂性:超大规模SoC设计带来的功能验证、时序收敛、功耗一致性签核等挑战。

- 高速信号完整性:400G及以上速率接口的SerDes设计、封装与PCB协同设计挑战。

- 软硬件协同:芯片SDK、驱动、与上层SDN控制器(如ONOS、ODL)的对接开发至关重要。

- 生态建设:需要与高校用户、设备制造商、软件开发商紧密合作,共同构建基于新芯片的校园网应用生态。

五、结论

面向校园网系统集成的定制化集成电路设计,是从根源上提升网络性能、灵活性及安全性的关键路径。通过设计CNIFC这类高度集成、智能可编程的芯片,不仅能为校园网注入强大的核心动力,更能为网络技术创新和“网络+教育”融合应用提供坚实的硬件底座,推动智慧校园向更深层次发展。尽管面临技术与管理上的挑战,但其带来的长期性能优势、运维简化与成本效益,使其成为未来校园基础网络建设值得投入的战略方向。