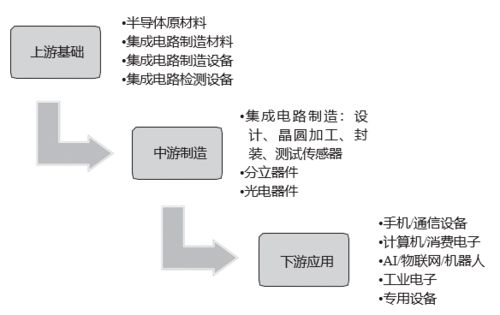

同步数字体系(SDH)是现代光通信网络的核心技术之一,其开销字节承载了丰富的管理与控制信息,对网络的运行、管理与维护至关重要。为满足高速、高可靠性的处理需求,设计一款专用的SDH开销处理集成电路(ASIC)成为提升系统性能的关键。本文旨在探讨SDH开销处理专用集成电路的设计流程、核心模块与实现要点。

一、设计背景与需求分析

SDH帧结构中的段开销(SOH)和通道开销(POH)包含了告警、性能监测、公务通信、数据通信通道(DCC)等重要信息。传统的软件或通用处理器处理方式在高速率(如STM-16及以上)场景下,往往面临吞吐量不足和实时性差的挑战。因此,专用集成电路的设计目标在于实现高速率(如2.5Gbps或更高)下的线速处理,具备低延迟、高可靠性、灵活可配置等特点,并能集成到更大的传输设备芯片中。

二、总体架构设计

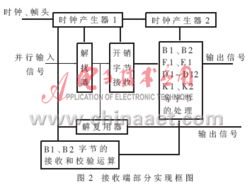

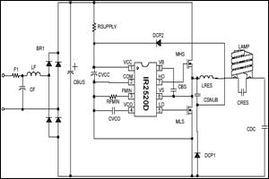

专用集成电路通常采用模块化、流水线设计思想。总体架构可划分为:

- 帧定位与同步模块:负责从高速串行数据流中识别并锁定SDH帧的起始位置,确保后续处理字节对齐。

- 开销字节提取/插入模块:根据配置,从特定时隙中提取开销字节供处理,或将处理后的开销字节插入回数据流。

- 核心处理引擎:这是设计的核心,通常包括:

- 告警检测与产生单元:实时监测如LOS、LOF、AIS、RDI等告警信号。

- 性能监视单元:对B1、B2、B3等字节进行误码计算与统计。

- 开销访问与处理单元:对DCC(D1-D12)、公务字节(E1、E2)、使用者通道字节(F1)等进行读写与交换控制。

- 指针处理单元:对于VC-n级别的开销,需处理AU/TU指针,完成同步与调整。

- 微处理器接口与控制寄存器组:提供与外部主控CPU(如ARM核)的接口(如APB、AHB总线),用于配置工作模式、查询状态、读取性能数据等。

- 时钟与复位管理模块:产生内部各模块所需的同步时钟,并管理全局及局部复位。

三、关键技术与设计挑战

- 高速数据接口设计:处理STM-N的高速串行数据流,需要精心设计串并转换、时钟数据恢复(CDR)电路,或与高速SerDes接口对接。

- 低延迟流水线:为确保处理不成为系统瓶颈,各功能模块需高度流水化,精心平衡各级流水深度,优化关键路径。

- 灵活可配置性:为适应不同网络设备和应用场景,开销处理的规则、映射路径等应可通过软件灵活配置,这增加了控制逻辑的复杂度。

- 时序收敛与低功耗设计:在深亚微米工艺下,确保高速时钟域下的时序收敛是一大挑战。需采用时钟门控、多电压域等低功耗设计技术。

- 验证的完备性:SDH协议复杂,开销处理场景繁多,需要构建分层验证环境,从模块级到系统级,结合定向测试与随机约束测试,确保功能百分百覆盖协议要求。

四、设计流程与实现

遵循标准的数字集成电路设计流程:

- 使用硬件描述语言(如Verilog HDL)进行RTL级设计与编码。

- 进行深入的功能仿真与验证。

- 逻辑综合,将RTL代码映射到目标工艺库的门级网表,进行时序约束与优化。

- 形式验证,确保综合前后逻辑功能一致性。

- 物理设计,包括布局规划、时钟树综合、布线、寄生参数提取、后仿真的物理验证等。

- 流片与测试。

五、

设计一款高性能的SDH开销处理专用集成电路,是一项涉及通信协议深度理解与先进集成电路设计技术的综合性工程。通过模块化架构、流水线技术、以及严谨的设计验证流程,可以实现满足高速光通信设备要求的专用芯片。此类芯片的成功设计,不仅能提升传输设备的集成度与性能,还能降低系统的整体功耗与成本,是光通信核心器件自主化的重要一环。随着网络速率向更高速率演进和SDH与OTN等技术的融合,开销处理ASIC的设计将面临更大的带宽、更灵活的处理能力以及更强的可编程性等新挑战。